# HT93LC46

# 1K 3-Wire CMOS Serial EEPROM

### **Features**

- Operating voltage V<sub>CC</sub>

- Read: 2.0V~5.5VWrite: 2.4V~5.5V

- Low power consumption

- Operating: 5mA max.

- Standby: 10μA max.

- · User selectable internal organization

- 1K(HT93LC46): 128×8 or 64×16

- 3-wire Serial Interface

- Write cycle time: 2ms max.

- Automatic erase-before-write operation

- Word/chip erase and write operation

- · Write operation with built-in timer

- Software controlled write protection

- 10-year data retention after 100K rewrite cycles

- 10<sup>6</sup> rewrite cycles per word

- 8-pin DIP/SOP package

- Commercial temperature range (0°C to +70°C)

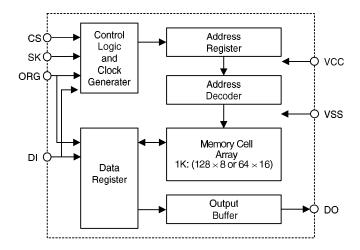

### **General Description**

The HT93LC46 is a 1K-bit low voltage nonvolatile, serial electrically erasable programmable read only memory device using the CMOS floating gate process. Its 1024 bits of memory are organized into 64 words of 16 bits each when the ORG pin is connected to VCC or organized into 128 words of 8 bits each when it is tied to VSS. The

device is optimized for use in many industrial and commercial applications where low power and low voltage operation are essential. By popular microcontroller, the versatile serial interface including chip select (CS), serial clock (SK), data input (DI) and data output (DO) can be easily controlled.

### **Block Diagram**

1

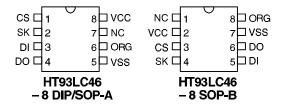

# **Pin Assignment**

# **Pin Description**

| Pin Name | I/O | Description           |  |  |  |

|----------|-----|-----------------------|--|--|--|

| CS       | I   | Chip select input     |  |  |  |

| SK       | I   | erial clock input     |  |  |  |

| DI       | I   | Serial data input     |  |  |  |

| DO       | О   | erial data output     |  |  |  |

| VSS      | I   | Negative power supply |  |  |  |

| ORG      | I   | nternal Organization  |  |  |  |

| NC       | _   | No connection         |  |  |  |

| VCC      | I   | Positive power supply |  |  |  |

### **Absolute Maximum Ratings**

| Operation Temperature (Commercial)                  | 0°C to 70°C                                    |

|-----------------------------------------------------|------------------------------------------------|

| Applied V <sub>CC</sub> Voltage with Respect to VSS | 0.3V to 6.0V                                   |

| Applied Voltage on any Pin with Respect to VSS      | V <sub>SS</sub> -0.3V to V <sub>CC</sub> +0.3V |

| Supply READ Voltage                                 | 2V to 5.5V                                     |

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

### **D.C. Characteristics**

| c 1 1            | D .                        | T               | est Conditions                                              | 3.51                 |      | 3.5                | Unit |

|------------------|----------------------------|-----------------|-------------------------------------------------------------|----------------------|------|--------------------|------|

| Symbol           | Parameter                  | V <sub>CC</sub> | Conditions                                                  | Min.                 | Тур. | Max.               |      |

| * 7              | 0                          |                 | Read                                                        | 2.0                  | _    | 5.5                | V    |

| Vcc              | Operating Voltage          | _               | Write                                                       | 2.4                  | _    | 5.5                | V    |

| I <sub>CC1</sub> | Operating Current (TTL)    | 5V              | DO unload,<br>SK=1MHz                                       | _                    | _    | 5                  | mA   |

| $I_{CC2}$        | Operating Current          | 5V              | DO unload,<br>SK=1MHz                                       | _                    | _    | 5                  | mA   |

|                  | (CMOS)                     | 2~5.5V          | DO unload,<br>SK=250kHz                                     | _                    | _    | 5                  | mA   |

| Istb             | Standby Current<br>(CMOS)  | 5V              | CS=SK=DI=0V                                                 | _                    | _    | 10                 | μΑ   |

| $I_{LI}$         | Input Leakage<br>Current   | 5V              | V <sub>IN</sub> =V <sub>SS</sub> ~V <sub>CC</sub>           | 0                    | _    | 1                  | μΑ   |

| $I_{LO}$         | Output Leakage<br>Current  | 5V              | V <sub>OUT</sub> =V <sub>SS</sub> ~V <sub>CC</sub><br>CS=0V | 0                    | _    | 1                  | μΑ   |

| V <sub>IL</sub>  | T . T . T/ 1/2 .           | 5V              | _                                                           | 0                    | _    | 0.8                | V    |

|                  | Input Low Voltage          | 2~5.5V          | _                                                           | 0                    | _    | 0.1V <sub>CC</sub> | V    |

| V <sub>IH</sub>  | Torrest III als IV-14 - 4- | 5V              | _                                                           | 2                    | _    | Vcc                | V    |

|                  | Input High Voltage         | 2~5.5V          | _                                                           | 0.9V <sub>CC</sub>   | _    | Vcc                | V    |

| Vol              | Output I ou Voltogo        | 5V              | I <sub>OL</sub> =2.1mA                                      | _                    | _    | 0.4                | V    |

|                  | Output Low Voltage         | 2~5.5V          | $I_{OL}$ =10 $\mu$ A                                        | _                    | _    | 0.2                | V    |

| Vон              | Output High Voltage        | 5V              | Ι <sub>ΟΗ</sub> =-400μΑ                                     | 2.4                  | _    |                    | V    |

|                  | Output High Voltage        | 2~5.5V          | Ι <sub>ΟΗ</sub> =-10μΑ                                      | V <sub>CC</sub> -0.2 | _    | _                  | V    |

| C <sub>IN</sub>  | Input Capacitance          | _               | V <sub>IN</sub> =0V, f=250kHz                               | _                    | _    | 5                  | pF   |

| C <sub>OUT</sub> | Output Capacitance         | _               | V <sub>OUT</sub> =0V, f=250kHz                              |                      | _    | 5                  | pF   |

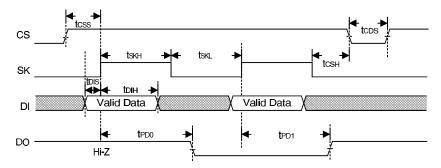

### A.C. Characteristics

| Cymbol           | Danamatan         | VCC=5V±10% |      | VCC=3V±10% |      | VCC=2V* |      | Unit  |  |

|------------------|-------------------|------------|------|------------|------|---------|------|-------|--|

| Symbol           | Parameter         | Min.       | Max. | Min.       | Max. | Min.    | Max. | Oiiit |  |

| $f_{SK}$         | Clock Frequency   | 0          | 2000 | 0          | 500  | 0       | 250  | kHz   |  |

| t <sub>SKH</sub> | SK High Time      | 250        | _    | 1000       | _    | 2000    | _    | ns    |  |

| tskl             | SK Low Time       | 250        | _    | 1000       | _    | 2000    | _    | ns    |  |

| tcss             | CS Setup Time     | 50         | _    | 200        | _    | 200     | _    | ns    |  |

| tcsh             | CS Hold Time      | 0          | _    | 0          | _    | 0       | _    | ns    |  |

| t <sub>CDS</sub> | CS Deselect Time  | 250        | _    | 250        | _    | 1000    | _    | ns    |  |

| t <sub>DIS</sub> | DI Setup Time     | 100        | _    | 200        | _    | 400     | _    | ns    |  |

| t <sub>DIH</sub> | DI Hold Time      | 100        | _    | 200        | _    | 400     | _    | ns    |  |

| t <sub>PD1</sub> | DO Delay to "1"   | _          | 250  | _          | 1000 | _       | 2000 | ns    |  |

| t <sub>PD0</sub> | DO Delay to "0"   | _          | 250  | _          | 1000 | _       | 2000 | ns    |  |

| tsv              | Status Valid Time | _          | 250  | _          | 250  | _       | _    | ns    |  |

| t <sub>HV</sub>  | DO Disable Time   | 100        | _    | 400        | _    | 400     | _    | ns    |  |

| tpR              | Write Cycle Time  | _          | 2    | _          | 2    | _       | _    | ms    |  |

<sup>\*</sup> For Read Operating Only

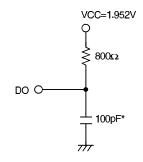

### A.C. test conditions

Input rise and fall time: 5ns (1V to 2V) Input and output timing reference levels: 1.5V

Output load: See Figure right

\*Including scope and jig

Output load circuit

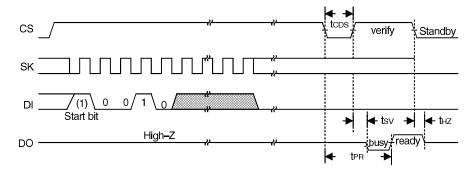

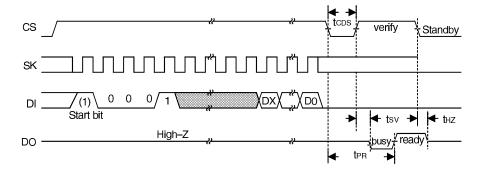

### **Timing Diagrams**

### **Functional Description**

The HT93LC46 is accessed via a three-wire serial communication interface. The device is arranged into 64 words by 16 bits or 128 words by 8 bits depending whether the ORG pin is connected to VCC or VSS. The HT93LC46 contains seven instructions: READ, ERASE, WRITE, EWEN, EWDS, ERAL and WRAL. When the user selectable internal organization is arranged into  $64\times16$  ( $128\times8$ ), these instructions are all made up of 9(10) bits data: 1 start bit, 2 op code bits and 6(7) address bits.

By using the control signal CS, SK and data input signal DI, these instructions can be given to the HT93LC46. These serial instruction data presented at the DI input will be written into the device at the rising edge of SK. During the READ cycle, DO pin acts as the data output and during the WRITE or ERASE cycle, DO pin indicates the BUSY/READY status. When the DO pin is active for read data or as a BUSY/READY indicator the CS pin must be high; otherwise DO pin will be in a high-impedance state. For successful instructions, CS must be low once after the instruction is sent. After power on, the device is by default in the EWDS state. And, an EWEN instruction must be performed before any ERASE or WRITE instruction can be executed. The following are the functional descriptions and timing diagrams of all seven instructions.

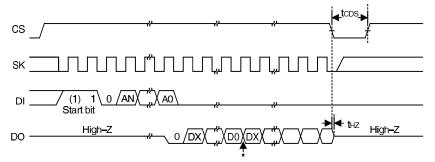

#### **READ**

The READ instruction will stream out data at a specified address on the DO pin. The data on DO pin changes during the low-to-high edge of SK signal. The 8 bits or 16 bits data stream is preceded by a logical "0" dummy bit. Irrespective of the condition of the EWEN or EWDS instruction, the READ command is always valid and independent of these two instructions. After the data word has been read the internal address will be automatically incremented by 1 allowing the next consecutive data word to be read out without entering further address data. The address will wrap around with CS High until CS returns to LOW.

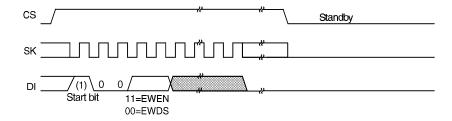

#### **EWEN/EWDS**

5

The EWEN/EWDS instruction will enable or disable the programming capabilities. At both the power on and power off state the device automatically entered the disable mode. Before a WRITE, ERASE, WRAL or ERAL instruction is given, the programming enable instruction EWEN must be issued, otherwise the ERASE/WRITE instruction is invalid. After the EWEN instruction is issued, the programming enable condition remains until power is turned off or a EWDS instruction is given. No data can be written into the device in the programming disabled state. By so doing, the internal memory data can be protected.

#### **ERASE**

The ERASE instruction erases data at the specified addresses in the programming enable mode. After the ERASE op-code and the specified address have been issued, the data erase is activated by the falling edge of CS. Since the internal auto-timing generator provides all timing signals for the internal erase, so the SK clock is not required. During the internal erase, we can verify the busy/ready status if CS is high. The DO pin will remain low but when the operation is over, the DO pin will return to high and further instructions can be executed.

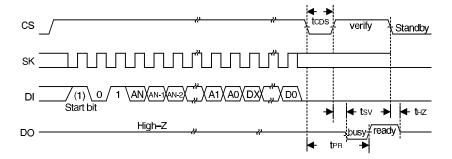

#### **WRITE**

The WRITE instruction writes data into the device at the specified addresses in the programming enable mode. After the WRITE opcode and the specified address and data have been issued, the data writing is activated by the falling edge of CS. Since the internal auto-timing generator provides all timing signal for the internal writing, so the SK clock is not required. The auto-timing write cycle includes an automatic erase-before-write capability. So, it is not necessary to erase data before the WRITE instruction. During the internal writing, we can verify the busy/ready status if CS is high. The DO pin will remain low but when the operation is over, the DO pin will return to high and further instructions can be executed.

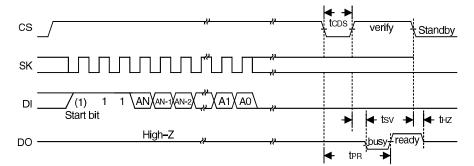

#### **ERAL**

The ERAL instruction erases the entire 64×16 or 128×8 memory cells to logical "1" state in the programming enable mode. After the erase-all instruction set has been issued, the data erase feature is activated by the falling edge of CS. Since the internal auto-timing generator provides all timing signal for the erase-all operation, so the SK clock is not required. During the internal erase-all operation, we can verify the busy/ready status if CS is high. The DO pin will remain low but when the operation is over, the DO pin will return to high and further instruction can be executed.

#### WRAL

The WRAL instruction writes data into the entire  $64{\times}16$  or  $128{\times}8$  memory cells in the programming enable mode. After the write-all instruction set has been issued, the data writing is activated by the falling edge of CS. Since the internal auto-timing generator provides all timing signals for the write-all operation, so the SK clock is not required. During the internal write-all operation, we can verify the busy/ready status if CS is high. The DO pin will remain low but when the operation is over the DO pin will return to high and further instruction can be executed.

# **Timing Diagrams**

### **READ**

\* Address pointer automatically cycles to the next word

| Mode | (X16)      | (X8)       |

|------|------------|------------|

| AN   | <b>A</b> 5 | <b>A</b> 6 |

| DX   | D15        | D7         |

### **EWEN/EWDS**

### WRITE

### **ERASE**

### **ERAL**

### WRAL

# **Instruction Set Summary**

### HT93LC46

| Instruction | Comments            | Start<br>bit | Op<br>Code | Address<br>ORG=0 ORG=1<br>X8 X16 | Data<br>ORG=0 ORG=1<br>X8 X16 |  |

|-------------|---------------------|--------------|------------|----------------------------------|-------------------------------|--|

| READ        | Read data           | 1            | 10         | A6~A0 A5~A0                      | D7~D0 D15~D0                  |  |

| ERASE       | Erase data          | 1            | 11         | A6~A0 A5~A0                      | _                             |  |

| WRITE       | Write data          | 1            | 01         | A6~A0 A5~A0                      | D7~D0 D15~D0                  |  |

| EWEN        | Erase/Write Enable  | 1            | 00         | 11XXXXX 11XXXX                   | _                             |  |

| EWDS        | Erase/Write Disable | 1            | 00         | 00XXXXX 00XXXX                   | _                             |  |

| ERAL        | Erase All           | 1            | 00         | 10XXXXX 10XXXX                   | _                             |  |

| WRAL        | Write All           | 1            | 00         | 01XXXXX 01XXXX                   | D7~D0 D15~D0                  |  |

Note: X stands for "don't care"

9 6th May '99

#### Holtek Semiconductor Inc. (Headquarters)

No.3, Creation Rd. II, Science-based Industrial Park, Hsinchu, Taiwan

Tel: 886-3-563-1999 Fax: 886-3-563-1189

#### Holtek Semiconductor Inc. (Sales Office)

11F, No.576, Sec.7 Chung Hsiao E. Rd., Taipei, Taiwan

Tel: 886-2-2782-9635 Fax: 886-2-2782-9636

Fax: 886-2-2782-7128 (International sales hotline)

#### Holtek Semiconductor (Shanghai) Inc.

7th Floor, Building 2, No.889, Yi Shan Rd., Shanghai, China

Tel: 021-6485-5560 Fax: 021-6485-0313

#### Holtek Semiconductor (Hong Kong) Ltd.

$\overline{\text{RM.711}},$  Tower 2, Cheung Sha $\overline{\text{Wan}}$  Plaza, 833 Cheung Sha Wan Rd., Kowloon, Hong Kong

Tel: 852-2-745-8288 Fax: 852-2-742-8657

#### Holmate Semiconductor, Inc.

48531 Warm Springs Boulevard, Suite 413, Fremont, CA 94539

Tel: 510-252-9880 Fax: 510-252-9885

### Copyright © 1999 by HOLTEK SEMICONDUCTOR INC.

The information appearing in this Data Sheet is believed to be accurate at the time of publication. However, Holtek assumes no responsibility arising from the use of the specifications described. The applications mentioned herein are used solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable without further modification, nor recommends the use of its products for application that may present a risk to human life due to malfunction or otherwise. Holtek reserves the right to alter its products without prior notification. For the most up-to-date information, please visit our web site at http://www.holtek.com.tw.